Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

Tags

- VMware #Shared Folder

- XTU #Virtual Machine System

- 매크로렌즈 #리버스링

- Dell #Latitude #BIOS

- Callaway #Mavrik #Epic Flash

- CM-EF-NEX

- 피코프레소 #ITOP40

- VirtualBox #VMware

- centos7 #yum update #/boot

- cycloidal #rv reducer

- Octave #homebrew #macOS

- Arduino #Wall Plotter

- Java #MacBook #macOS

- ESP32 #Arduino

- macro lens #EF #FD

- k6 #피코프레소

- Tarantula #3D 프린터

- VNC #Firewall #CenOS7 #VMware

- Xeon #E5-2680

- Oh My Zsh #macOS

- x99 itx/ac

- ITOP40

- fat32 #rufus

- 다이슨 #배터리

- Laptop #CPUID

- Linux #VirtualBox

- Arduino #PlatformIO #macOS

- razer #deathadder #viper #g102

- TensorFlow #Python #pip

- egpu #aorus gaming box #gtx1070 #tb3

Archives

- Today

- Total

얕고 넓게

[FPGA] ZCU102: PL Clock, Reset 설정 본문

2025.03.13

ZYBO Z7과는 다르게 PL용 Single-ended Clock이 없는 것 같다.

ZYBO용 PL LED를 돌리면 동작하지 않는다.

클럭 설정을 하여 확인한 결과

PL 용 clock은 clk_74_25, clk_125 같음

clk_74_25 bank44

clk_125 bank47

Copilot을 통해 diff2single code 확인

module differential_to_single_ended (

input wire clk_p, // Differential clock positive

input wire clk_n, // Differential clock negative

output wire clk_out // Single-ended clock output

);

wire clk_ibufds;

// Instantiate the IBUFDS primitive

IBUFDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IBUF_LOW_PWR("TRUE"), // Low power (TRUE) vs. performance (FALSE) setting for the I/O buffer

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFDS_inst (

.I(clk_p), // Connect positive differential input

.IB(clk_n), // Connect negative differential input

.O(clk_ibufds) // Single-ended clock output

);

assign clk_out = clk_ibufds;

endmodule

module led_stream(

output reg [3:0] led, // LED4 to LED1, 1 on, 0 off

input clk_74_25_p, // FPGA PL clock, 50 MHz

input clk_74_25_n, // FPGA PL clock, 50 MHz

input rst // FPGA reset pin

);

reg [31:0] cnt;

reg [1:0] led_on_number;

//clock input 50000000

parameter CLOCK_FREQ =50000000;

parameter COUNTER_MAX_CNT=CLOCK_FREQ/2-1;//change time 0.5s

wire clk_74_25;

// Instantiate the differential to single-ended converter

differential_to_single_ended diff_to_single (

.clk_p(clk_74_25_p),

.clk_n(clk_74_25_n),

.clk_out(clk_74_25)

);create_clock -period 13.468 -name clk_sys [get_ports clk_74_25_p]

set_property CLOCK_DEDICATED_ROUTE ANY_CMT_COLUMN [get_nets clk_sys]

## Sys clock

set_property -dict {PACKAGE_PIN AK14 IOSTANDARD LVDS_25} [get_ports clk_74_25_n]

set_property -dict {PACKAGE_PIN AK15 IOSTANDARD LVDS_25} [get_ports clk_74_25_p]

...

## LEDs

set_property -dict {PACKAGE_PIN AG14 IOSTANDARD LVCMOS33} [get_ports {led[3]}]

set_property -dict {PACKAGE_PIN AF13 IOSTANDARD LVCMOS33} [get_ports {led[2]}]

set_property -dict {PACKAGE_PIN AE13 IOSTANDARD LVCMOS33} [get_ports {led[1]}]

set_property -dict {PACKAGE_PIN AJ14 IOSTANDARD LVCMOS33} [get_ports {led[0]}]

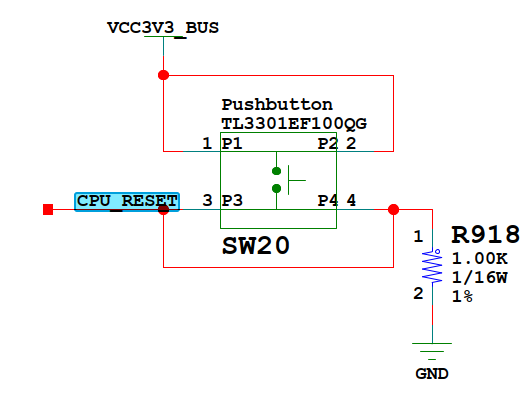

Reset 을 없애면 LED가 동작, 혹시나 싶어서 Polarity 확인

24 SW20 aUser I/O (CPU_RESET pushbutton switch, Active-High) E-Switch TL3301EP100QG 53

CPU Reset Pushbutton (Active‐High) AM13 CPU_RESET LVCMOS33 SW20.3

Active High 같다.

Verilog, xdc 수정

always @(posedge clk_74_25, posedge rst) begin

if(rst) begin

cnt <= 32'd0;

led_on_number <= 2'd0;

end

else begin

cnt <= cnt + 1'b1;

if(cnt == COUNTER_MAX_CNT) begin//����0.5s

cnt <= 32'd0;

led_on_number <= led_on_number + 1'b1;

end

end

end# reset

set_false_path -from [get_ports rst]

set_property -dict {PACKAGE_PIN AM13 IOSTANDARD LVCMOS33} [get_ports rst]

결론

- Clock

- PL용 사용 clk_74_25, clk_125

- diff2single 변환 필요

- xdc에 LVDS_25 p/n

- Reset

- CPU_RESET 사용

- active-high

추가로 125MHz 테스트

일단 이름은 그대로 두고 핀만 바꿔서 테스트

## Sys clock

set_property -dict {PACKAGE_PIN F21 IOSTANDARD LVDS_25} [get_ports clk_74_25_n]

set_property -dict {PACKAGE_PIN G21 IOSTANDARD LVDS_25} [get_ports clk_74_25_p]clk_125 핀도 정상 동작

'IT > FPGA' 카테고리의 다른 글

| [FPGA] Vivado Programmer @MacBook (Arm) (0) | 2025.03.24 |

|---|---|

| [FPGA] ZCU102: VPG-HDMI (0) | 2025.03.13 |

| [FPGA] ZYBO Z7: VPG (0) | 2025.03.12 |

| [FPGA] ZYNQ Mini 정보, Vivado 2024.2 (0) | 2025.02.02 |

| [FPGA] 부품 가격@2010 (0) | 2022.06.07 |