Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

Tags

- VirtualBox #VMware

- Linux #VirtualBox

- Octave #homebrew #macOS

- ITOP40

- Dell #Latitude #BIOS

- cycloidal #rv reducer

- fat32 #rufus

- centos7 #yum update #/boot

- x99 itx/ac

- Arduino #PlatformIO #macOS

- Tarantula #3D 프린터

- Java #MacBook #macOS

- Xeon #E5-2680

- XTU #Virtual Machine System

- 매크로렌즈 #리버스링

- 피코프레소 #ITOP40

- razer #deathadder #viper #g102

- Arduino #Wall Plotter

- Laptop #CPUID

- macro lens #EF #FD

- Callaway #Mavrik #Epic Flash

- VNC #Firewall #CenOS7 #VMware

- k6 #피코프레소

- VMware #Shared Folder

- ESP32 #Arduino

- Oh My Zsh #macOS

- egpu #aorus gaming box #gtx1070 #tb3

- TensorFlow #Python #pip

- CM-EF-NEX

- 다이슨 #배터리

Archives

- Today

- Total

얕고 넓게

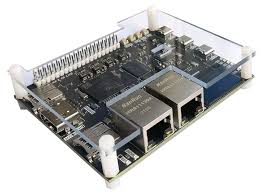

[FPGA] ZYNQ Mini 정보, Vivado 2024.2 본문

205.02.02

Microsoft OneDrive

onedrive.live.com

기본

- +5V Must

- Main Power: Type-C@JTAG

- Boot Mode

- UU(00): JTAG

- DU(10): QSPI, from FLASH, OLED Demo, Heat!!!

- DD(11): SD Card, petalinux

- Petalinux

- microSD, FAT32

- 02 Routine Project > "LINUX part \01petalinux2018.3 run \compiled boot

file" - BOOT.BIN, image.ub

- UART port

- 115200, 8, none, 1, no flow control

- root/root

잘 동작하는지 보기위해 QSPI모드로 하고 Power Meter가 달린 USB-C 케이블 연결-> 1.-W

전력은 크지 않은데 보드 뒤면이 점점 따뜻해 진다.

방열판 필요한데...

문서에서 Vivado 2018.3 버전을 사용하라고 한다.

AMD 홈펭이지에 Vivado Lab Version은 라이센스 필요없다고 하고 파일크기도 1GB 미만이다.

-> 이건 프로그래밍만 가능 ㅠㅠ

2025.02.03

최신 버전의 Unified Install로 2024.2 설치했다.

Zynq 7010, 7020은 라이센스 없이도 빌드가 잘된다.

다운받은 파일에서 02_Creat project under VIVADO.pdf 를 따라하면 된다.

직접 코딩하고 핀 매핑해도 되지만 파일에 있는 *.v, *.xdc 를 보면

C:\Work\FPGA\ZYNQ_MINI_ New\03 Sample Projects\7010\FPGA部分\fpga_01_pl_led_stream

module led_stream(

output reg [3:0] led, // LED4 to LED1, 1 on, 0 off

input clk, // FPGA PL clock, 50 MHz

input rst_n // FPGA reset pin

);

reg [31:0] cnt;

reg [1:0] led_on_number;

//clock input 50000000

parameter CLOCK_FREQ =50000000;

parameter COUNTER_MAX_CNT=CLOCK_FREQ/2-1;//change time 0.5s

always @(posedge clk, negedge rst_n) begin

if(!rst_n) begin

cnt <= 32'd0;

led_on_number <= 2'd0;

end

else begin

cnt <= cnt + 1'b1;

if(cnt == COUNTER_MAX_CNT) begin//¼ÆÊý0.5s

cnt <= 32'd0;

led_on_number <= led_on_number + 1'b1;

end

end

end

always @(led_on_number) begin

case(led_on_number)

0: led <= 4'b0001;

1: led <= 4'b0010;

2: led <= 4'b0100;

3: led <= 4'b1000;

endcase

end

endmodule

set_property PACKAGE_PIN T12 [get_ports {led[3]}]

set_property PACKAGE_PIN U12 [get_ports {led[2]}]

set_property PACKAGE_PIN V12 [get_ports {led[1]}]

set_property PACKAGE_PIN W13 [get_ports {led[0]}]

set_property PACKAGE_PIN K17 [get_ports clk]

set_property PACKAGE_PIN M19 [get_ports rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]'IT > FPGA' 카테고리의 다른 글

| [FPGA] ZCU102: VPG-HDMI (0) | 2025.03.13 |

|---|---|

| [FPGA] ZYBO Z7: VPG (0) | 2025.03.12 |

| [FPGA] 부품 가격@2010 (0) | 2022.06.07 |

| [FPGA] ZYBO Z7: HDMI Pass Through (0) | 2022.02.13 |

| [FPGA] ZYBO Z7: OV5647 (라즈베리파이 ) (0) | 2022.02.13 |